LVDS SerDes

SerDes는 Serializer와 Deserializer의 앞 글자를 가지고 와서 만든 단어이다.

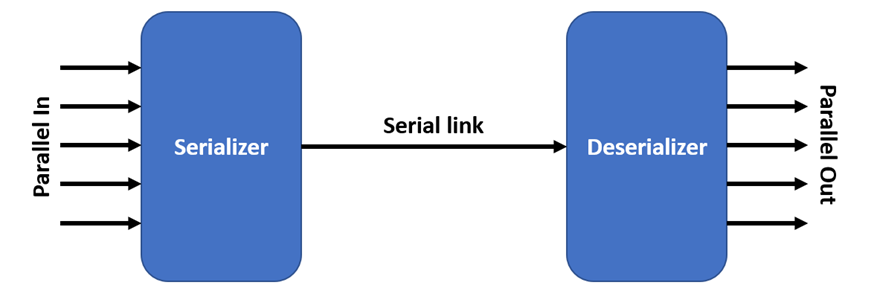

Fig 1. LVDS SerDes

위 그림을 카메라 링크 인터페이스와 비교해보면 Serializer 부분은 카메라, Serial link 부분은 LVDS, Deserializer 부분은 프레임 그래버라고 할 수 있다.

굳이 이렇게 병렬과 직렬 구조의 변환을 하는 이유는, 데이터 통신 시에는 병렬 통신보다 직렬 통신이 더 이점이 많기 때문이다. 예를 들면 카메라 링크의 경우 최대 80 bit 까지 통신하는데, 이를 병렬 통신으로 하면 단순히 생각했을 때 80개의 pin이 필요하게 된다. 하지만 직렬 통신의 경우 하나의 pin에 다수의 데이터 bit를 통신할 수 있으므로 pin 개수로부터 자유로워진다. 따라서 데이터 통신 상으로는 직렬로 통신하고, 카메라 혹은 프레임 그래버에서는 다시 병렬로 변환해준다.

이때 카메라 및 프레임 그래버에서 다시 병렬로 변환하는 이유는 clock 수와 관계 있다. 카메라 링크 인터페이스에서 LVDS SerDes는 7:1의 serialize를 거치는데, 이는 만약 7000번의 데이터를 획득하고 싶을 때 serial 통신의 경우 7000 Hz의 클럭 수가 필요하다. 하지만 7:1의 병렬 통신이라면 7000을 7로 나눠 1000 Hz 만으로도 충분하다. 즉, 클럭 수가 낮아진다는 이점이 있다.

그러나 LVDS의 단점으로는 이전에 언급한 skew 현상이 발생할 수 있다는 점이 있다. 이때 발생하는 Skew 현상의 종류는 두가지가 있는데 하나는 데이터와 데이터 간의 skew 현상이고 또 하나는 데이터와 clock 간의 skew 현상이다.

Fig 2. SerDes System

먼저 데이터와 데이터간의 skew 현상의 경우, aligner 라는 부분이 존재하여 이것이 skew 현상을 해결한다. FPGA 상에서 aligner가 데이터를 alignment하는 방법에는 여러가지가 있는데 그 중 한 가지로는 comma alignment가 있다.

Fig 3. Conceptual view of 10-bit comma alignment

Comma란, 데이터 송신부와 수신부간의 약속된 신호를 의미한다. 위 그림을 예로 들면 가장 오른쪽에서부터 차례로 데이터가 들어오고 있을 때, 아직 alignment 되지 않은 데이터 상태에서 comma data로 약속한 ‘0011111010’ 신호가 인식되면 그때부터 10-bit씩 데이터 align을 진행하는 방식이다.

데이터와 Clock간의 skew 현상의 경우 보완하는 방법은 두 가지가 있는데 첫번째는 Phase Locked-Loop이다.

Fig 4. Basic Phase Locked-Loop Composition

PLL(Phase Locked-Loop) 회로는 레퍼런스 클럭(reference clock)과 주파수, 위상차가 같은 클럭을 출력하는 회로이다.

Phase Frequency Detector, 즉 PFD는 레퍼런스 클럭과 분주기(Divider)의 출력으로 나오는 분주 클럭을 비교하는 부분이다. 분주 클럭이 레퍼런스 클럭보다 빠르면 down signal을 내보내 주파수를 낮추고, 분주 클럭이 레퍼런스 클럭보다 느리면 up signal을 내보내 주파수를 높이는 역할을 한다.

Charge pump 및 Low-pass filter는 이를 가능하게 해주는 부분이다. VCO는 입력 전압에 따라 출력 주파수를 조절하는 역할을 하기 때문에, CP 및 LPF에서 전압값을 높이거나 낮추는 것으로 주파수를 조절한다. 이런 식으로 진행하여 최종적으로 레퍼런스 클럭과 분주 클럭의 주파수와 위상이 같게 되었을 때 PLL 회로는 안정화된다.

클럭과 데이터 간의 skew 현상을 해결하는 두번째 방법으로는 오버 샘플링(Over Sampling)이 있다.

Fig 5. Over Sampling

예를 들어 클럭 주파수가 1000 Hz 라면, 그것의 3배를 해서 3000 Hz를 만들어 데이터를 3000번 획득한다. 이 경우 1000개 짜리 데이터 그룹이 총 3개가 생성되는 것인데, 그 중에서 기존의 데이터와 가장 가까운 값을 가지는 그룹을 선택해서 데이터를 획득하는 방식이 오버 샘플링이다.

클럭을 높이는 방식이기 때문에, 클럭 수가 낮을수록 좋은 데이터 통신 특성상 단점이 될 수 있지만 그 외에 좋은 다양한 이점이 있어 가능하면 clock data recovery 보다는 over sampling을 사용하려는 추세이다. 하지만 클럭 수가 높아지기 때문에 성능 좋은 FPGA가 필요하다는 점은 고려사항이다.

지금까지 우리는 LVDS, 그리고 SerDes에 대해서 알아보았다. 이 LVDS SerDes 5개를 가지고 이용하는 통신 기술이 Channel Link이며 이를 이용하는 것이 바로 카메라링크(CameraLink) 인터페이스다. 다음 시간에는 Channel Link에 대해서 알아본 뒤에 카메라링크의 다양한 configuration에 대해서 알아보겠다.

'인터페이스 > CameraLink' 카테고리의 다른 글

| Camera Link 4. Camera Signal Requirements (0) | 2023.07.24 |

|---|---|

| CameraLink 3. Channel Link, Configuration (0) | 2023.07.23 |

| CameraLink 1. LVDS 기술 (0) | 2023.07.17 |